今回はちょっとニッチな内容です.この記事では,Digilentが公開しているZybo Z7 Pcam 5C Demoを実際に動かして,簡易的な画像処理を付けたしてみます.当方初心者なので勉強しながら備忘録として書きます.間違ってたらごめんね.

この過程でDemoのIPを編集して機能を追加しますが,IPを編集して論理合成しても反映されない問題が発生したのでその記録を残します.

FPGAとは

FPGAは回路記述を行うことで自由な動作を実現できる論理回路の塊みたいな感じです.

実行環境

- Windows 10 Pro

- Vivado 2017.4.1

- 影響ないと思うけど4.1にアップデートしておきました.

使うもの

があったら動くと思う) - 5VACアダプタ - 最初これを忘れて動かなかった.USB給電では動かないので注意.1Aくらいあればなんでも大丈夫だと思います.自分は手持ちの3Aのやつを使いました.

DIGILENT zybo z7 : zynq-7000アーム/ FPGA Soc開発ボード Zybo Z7-20

- メディア: Personal Computers

秋月でカメラとZyboセットで安く売ってるのでこっちの方がいいかも. akizukidenshi.com

動かし方

動いてる仕組みとかはとりあえず置いといてとりま動かしてみます.

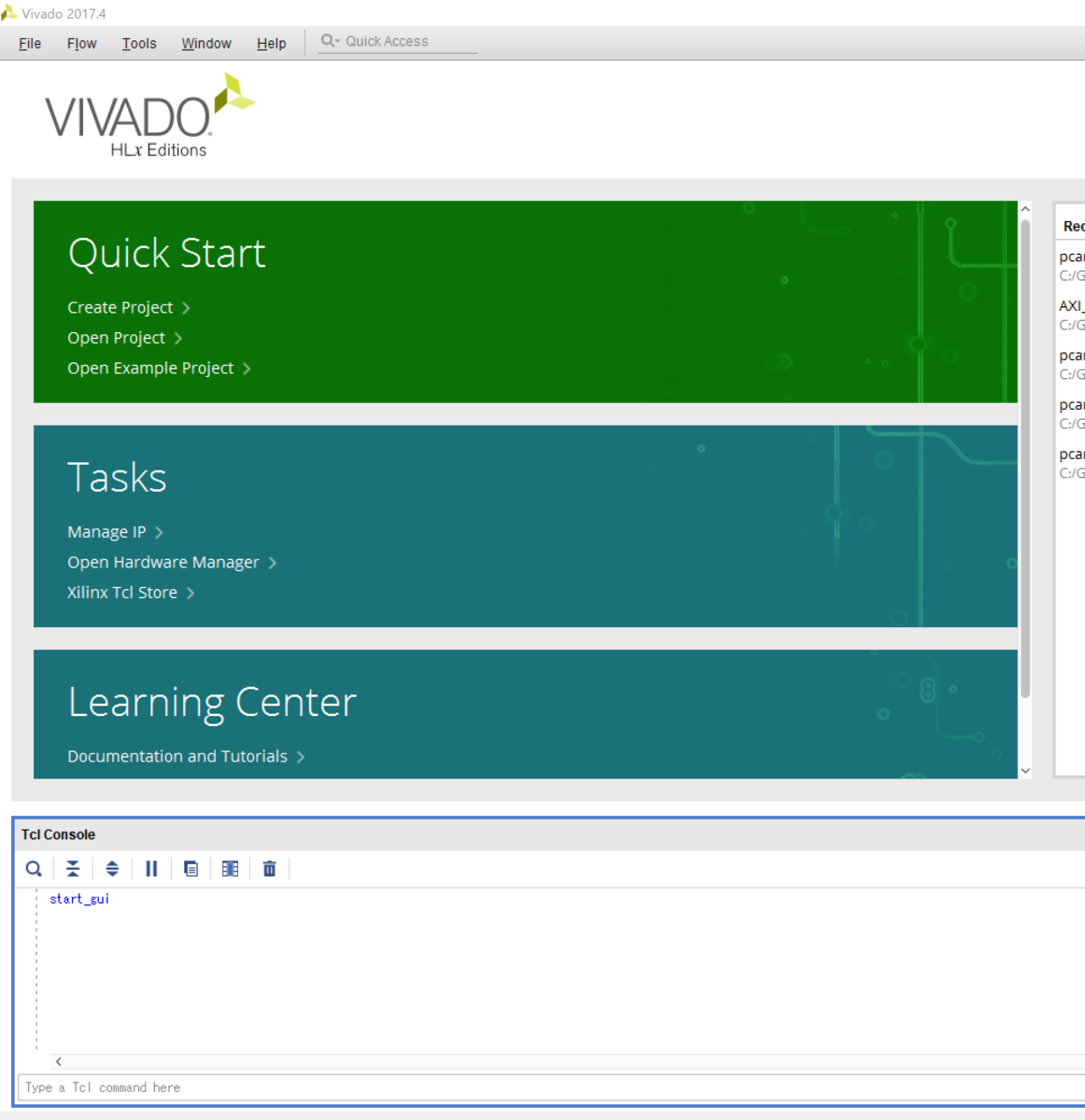

0 Vivadoをインストール

FPGAに書き込んだり論理合成するIDEのVivadoをインストールしてください.今回は2017.4を選択しました.もう2017はversionsに表示されてないのでアーカイブをクリックして2017.4を選択します.Vivado Design Suite - HLx Edition - 2017.4 Full Product Installationってやつです.インストーラのダウンロードにはXilinxアカウントが必須なので持っていない人は作りましょう.

インストーラを開くとまたログインを求められますのでログインしてください.その後インストールするエディションを選択させられます.今回は無償版でも大丈夫なのでWebPack版を選択しました.

1 プロジェクトをクローンしてくる

ここから2017をダウンロードしてきてください.ZIPを解凍しておきましょう.

2 プロジェクトを生成する

いよいよVivadoを使った作業が始まります.ちょっとわかりにくいですが,このでもプロジェクトはプロジェクトファイルが最初から入っているわけではなく自分で作成する必要があります.でも大丈夫,一つのコマンドだけで作成できます.

Vivadoを開くと下にTCL Consoleというのがあると思います.これを使ってプロジェクトを作ります.

Type a tcl...っというところで自分が先ほど展開したデモプロジェクトの/projまで移動します.自分はCドライブ直下にGitHubフォルダを作ってそこに展開したので

cd C:/Github/Zybo_Pcam/Zybo-Z7-20-pcam-5c/proj

と入力しました.WindowsではディレクトリをC:\hoge\hugaというように表現しますが,TCLではLinuxやMacのように/hoge/hugaと表現するので注意しましょう.要はバックスラッシュをスラッシュに置き換えて入力してください.

続いてプロジェクト生成を行います.

source ./create_project.tcl

と入力して実行します.しばらく待つとプロジェクトが作成されます.

3 論理合成する

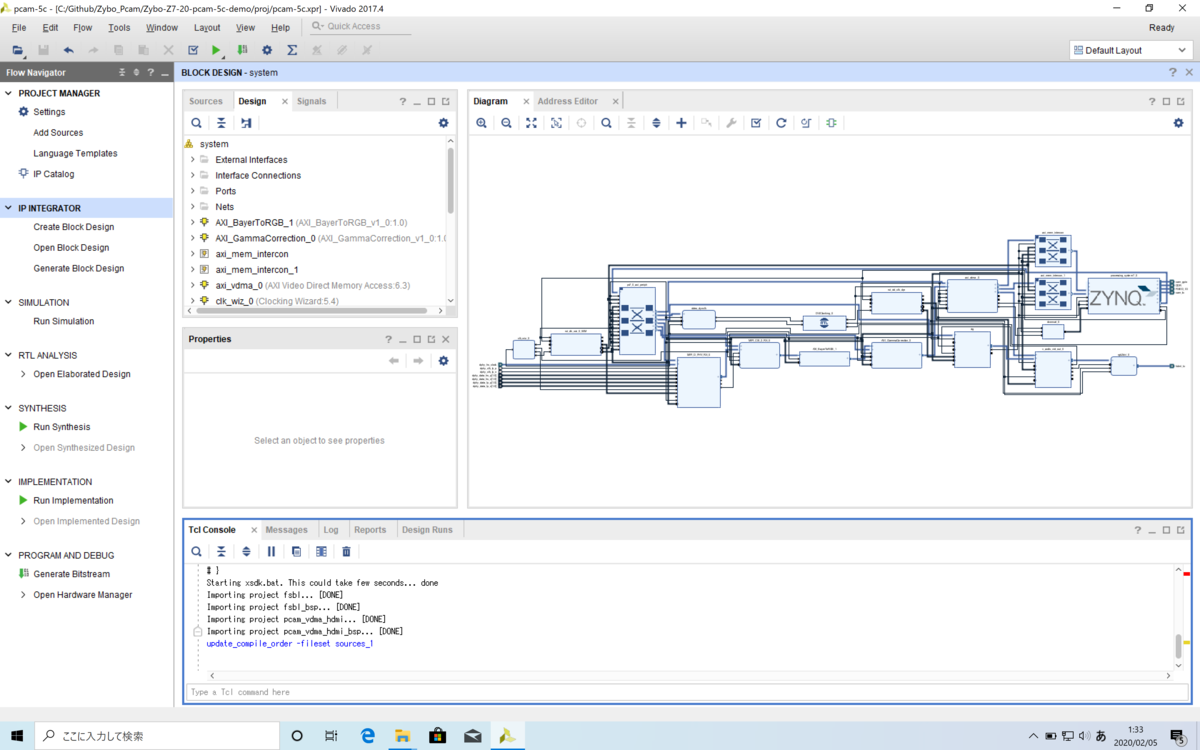

プロジェクトができたらこのような画面になります.これがこれから死ぬほどみていく画面になります.

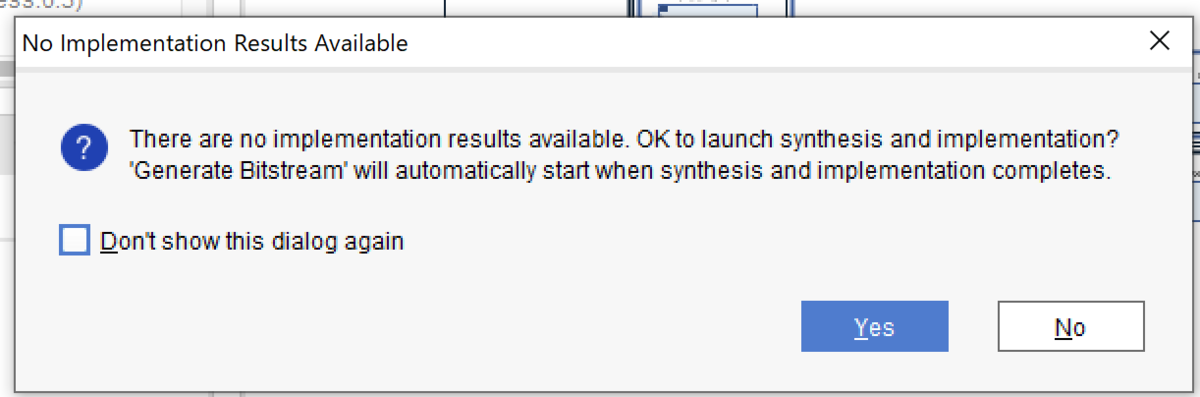

左のFlow Managerの一番下にあるGenerate Bitstreamをクリックします.このように聞かれますがYesをクリックしてください.

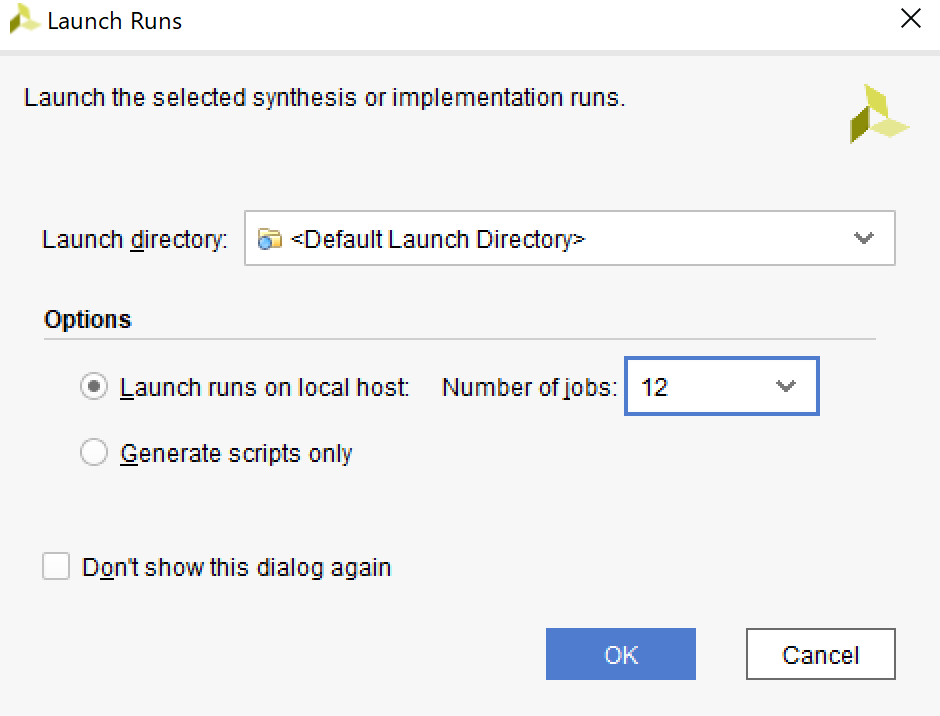

次にこのようになります.これもデフォルトのままOKをクリックします.これで論理合成が始まります.右上のReadyがRunnig…となることがわかります.

JOB数は使用環境によって変わってくるので気にしないでください.論理合成は環境によって5分〜30分程度かかることがあります.コーヒーブレイクでもしてください.パワフルなPC欲しくなりますね?

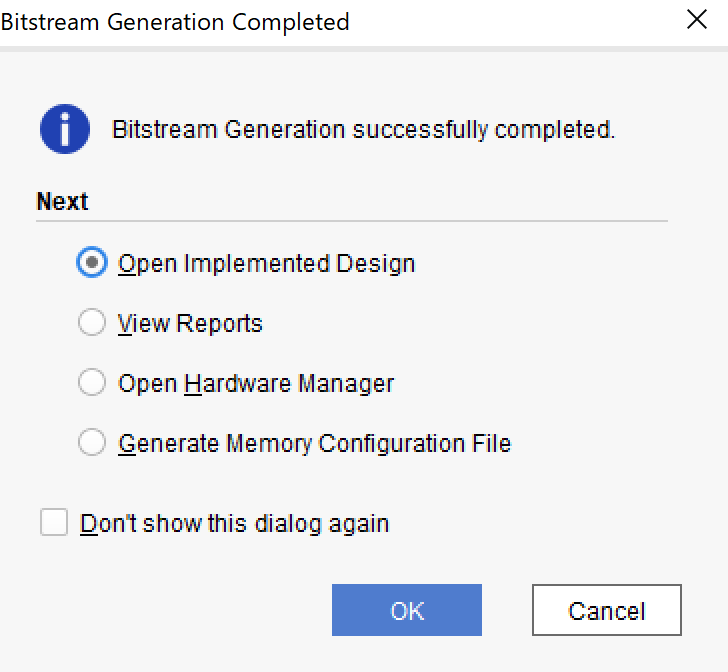

完了するとBitstream Successの表示がでます.ここでOKを押したくなりますが,Implementationは別にみたくないのでCancelで閉じます.

4 SDK

続いてSDKを起動します.ツールバーからFile-Export-Export Hardwareをクリック,Include BitstreamをチェックしてOKを押します.

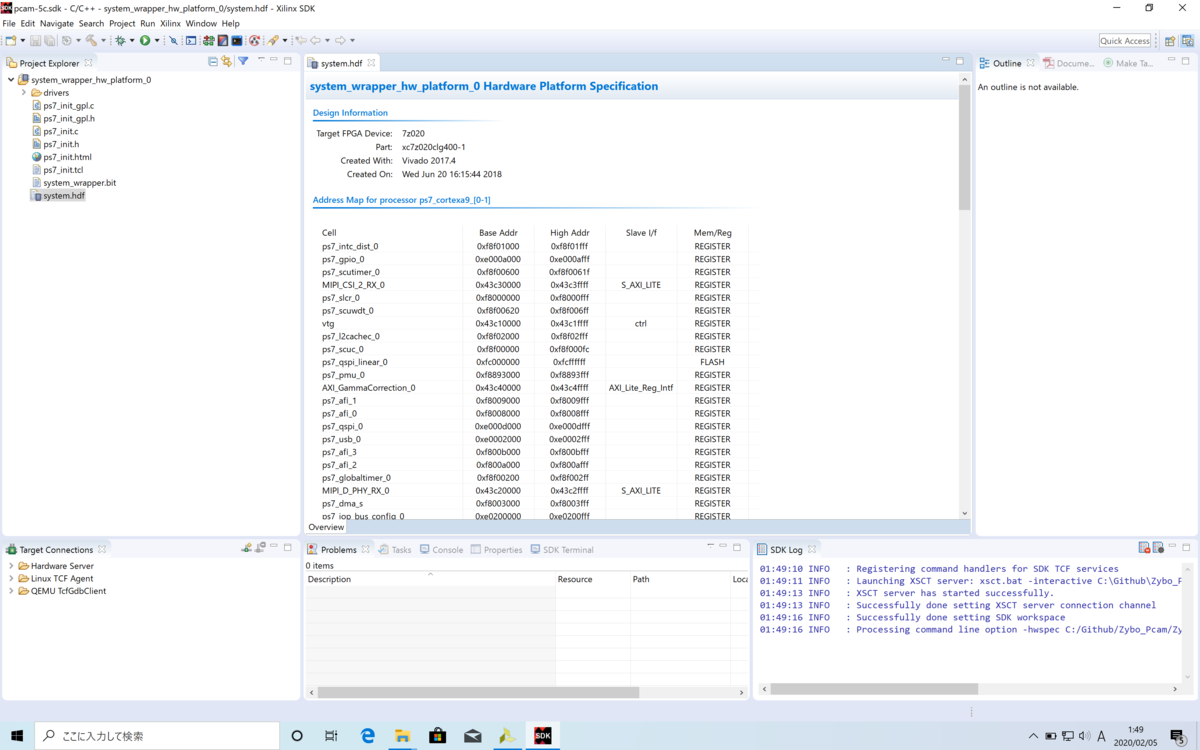

続いて同じくFile-Launch SDKをクリックします.ダイアログはデフォルトのままOKを押します.立ち上がるとこんな感じ.

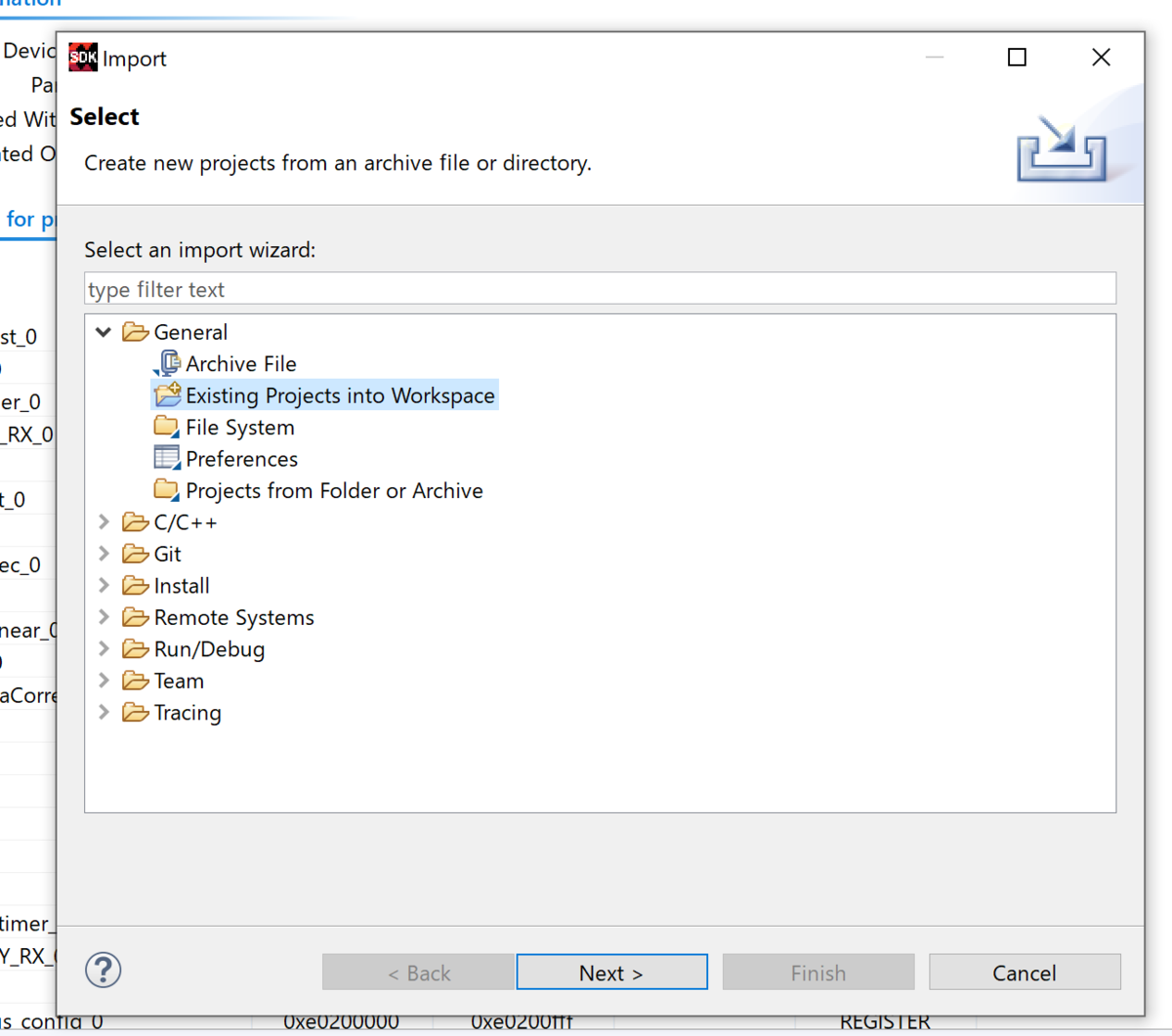

SDKのFileからImportをクリック,ダイアログではGeneral-Existing Projects…を選択してNEXTをクリック.

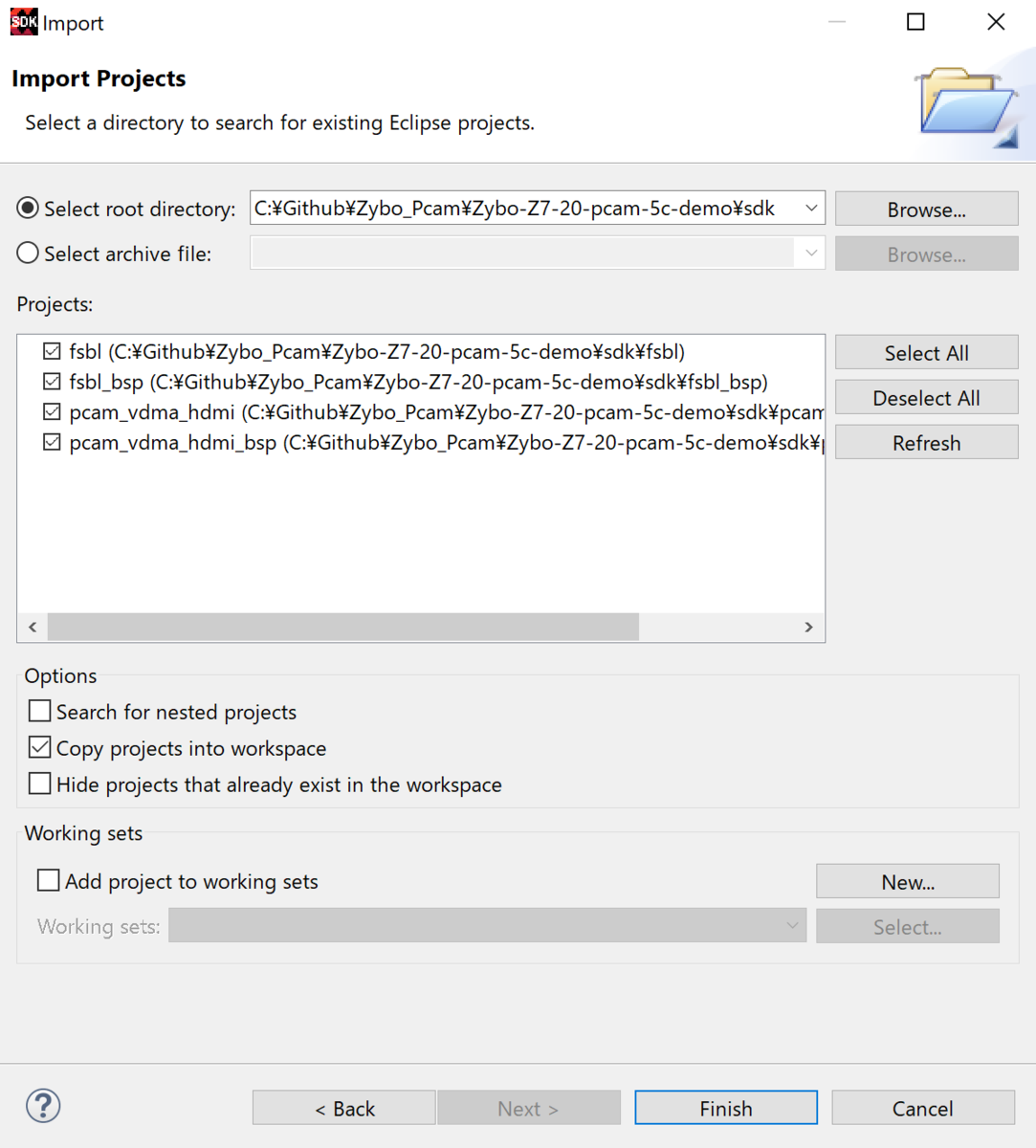

ディレクトリBrowseしてデモプロジェクトを展開した場所の/sdkを選択してOKを押します.copy into wordspaceにチェックを入れてFinish.するとSDKのProject managerに/sdkがインポートされます.

5 Zyboに書き込む

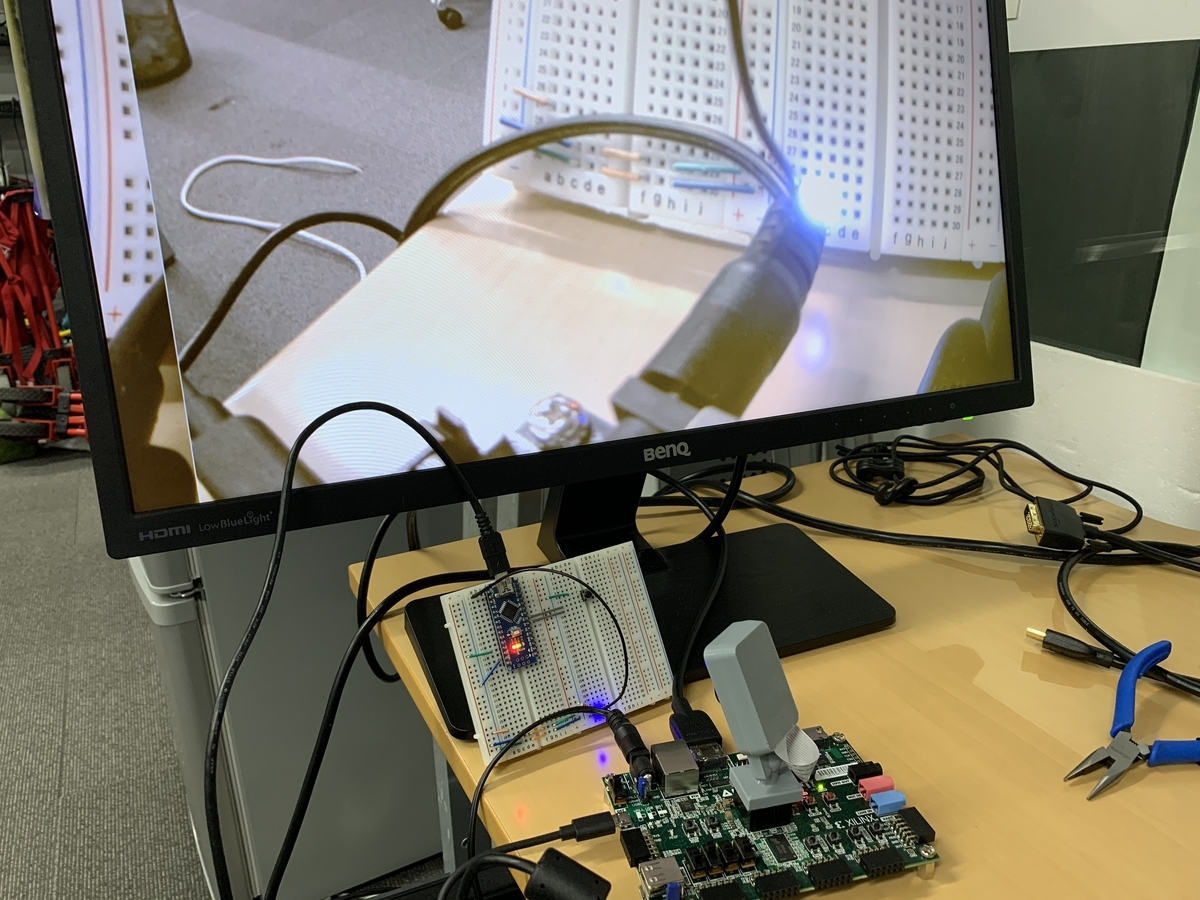

ようやくZyboに書き込みます.ZyboにHDMIケーブルを接続,ACアダプタを接続,PCとUSB接続します.電源選択のジャンパはACAdapterにしておかないとUSB給電のままになってしまいます.

SDKのProgram FPGAをクリック,そのままOKで書き込みます.USB接続しておけば認識されます.

次にProject managerのfsblを右クリックからrun asでlaunch on hardwareを選択します.書き込みが終わったら同様にcam_vdma_hdmiを右クリックからrun asでlaunch on hardwareを選択します.

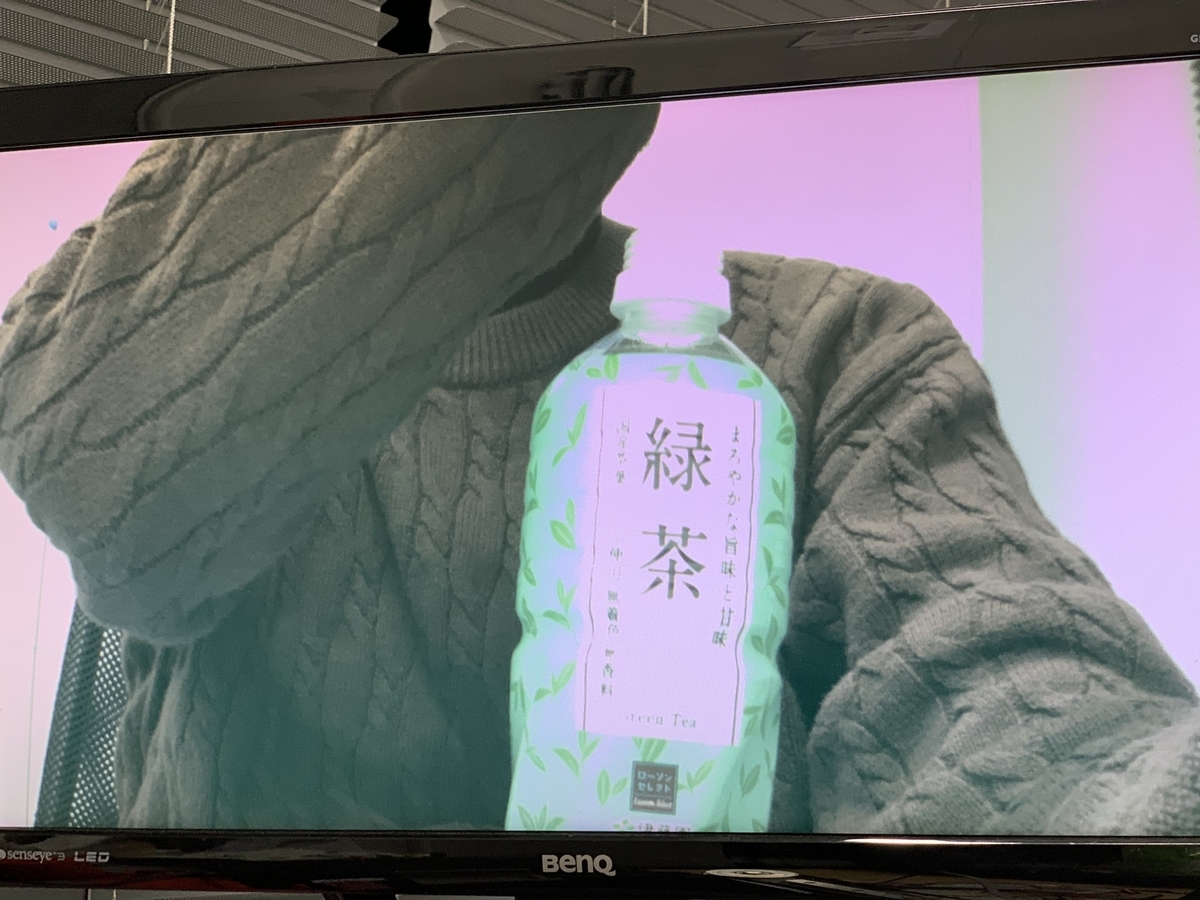

これでPcamの映像がHDMI出力されるはずです.ちょっと色がおかしいかも.自分はセピア調っぽくでました.あとで色調調整しないとダメだね.露光もオーバー気味.

6 カスタムする

さてここまでは普通にdemoをやっただけなので誰でもできるはず.ここからが問題です.ここでは,簡易的なカラーキーができるように改造してみることにします.

カラーキーっていうのはある指定した色のみを見えなくすることで,背景を透過することができるものです.クロマキーとかルミナンスキーとか色々あります.ニコニコとかでBB素材(Blue Background)とかGB素材(Green Background)とかあるじゃないですか.ああいうやつですね.今回はデモを改造してクロマキーとは言わずとも,ある特定の色にオーバーライドして色をつけられるようにしてみます.

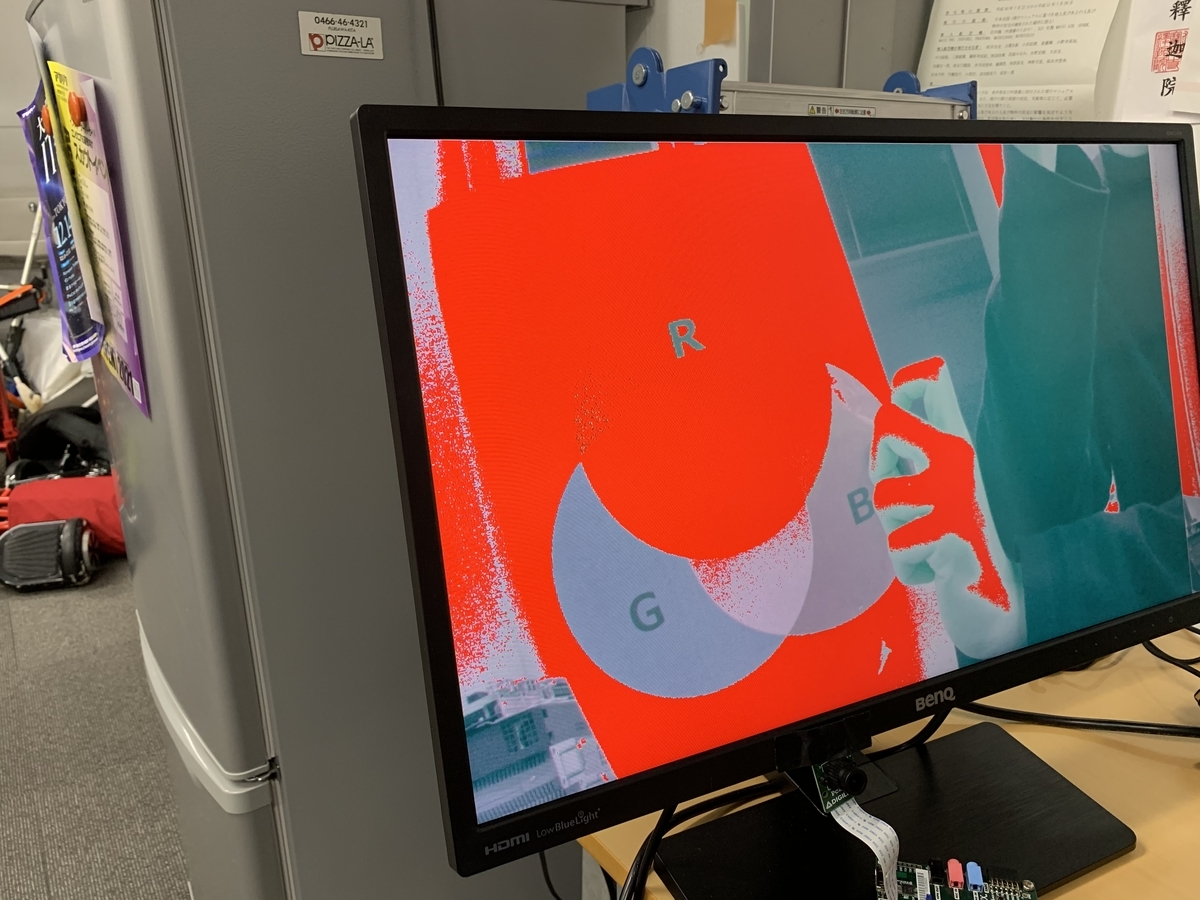

で,できたのがこちらです.(3分クッキング感)これは白っぽいところを赤く上書きして表示しています.露光オーバーのところが塗りつぶされてる感じですね.背景が若干抜けてるように見えるのでカラーキーということにしておいてください.

BayerToRGBをいじる

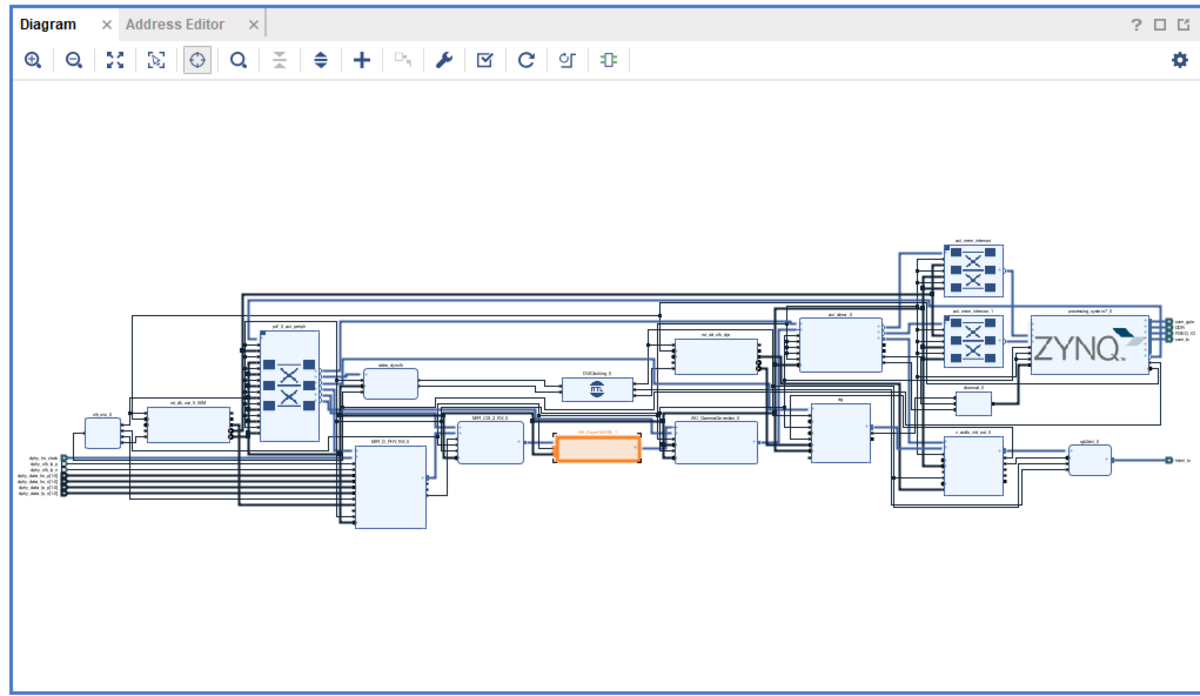

このようなカラーキーをやるためにはいろいろやり方が考えられますが,今回はUser IPの中のBayerToRGBを改造することにします.RTL Diagramでいうとこのハイライトされてるやつですね.

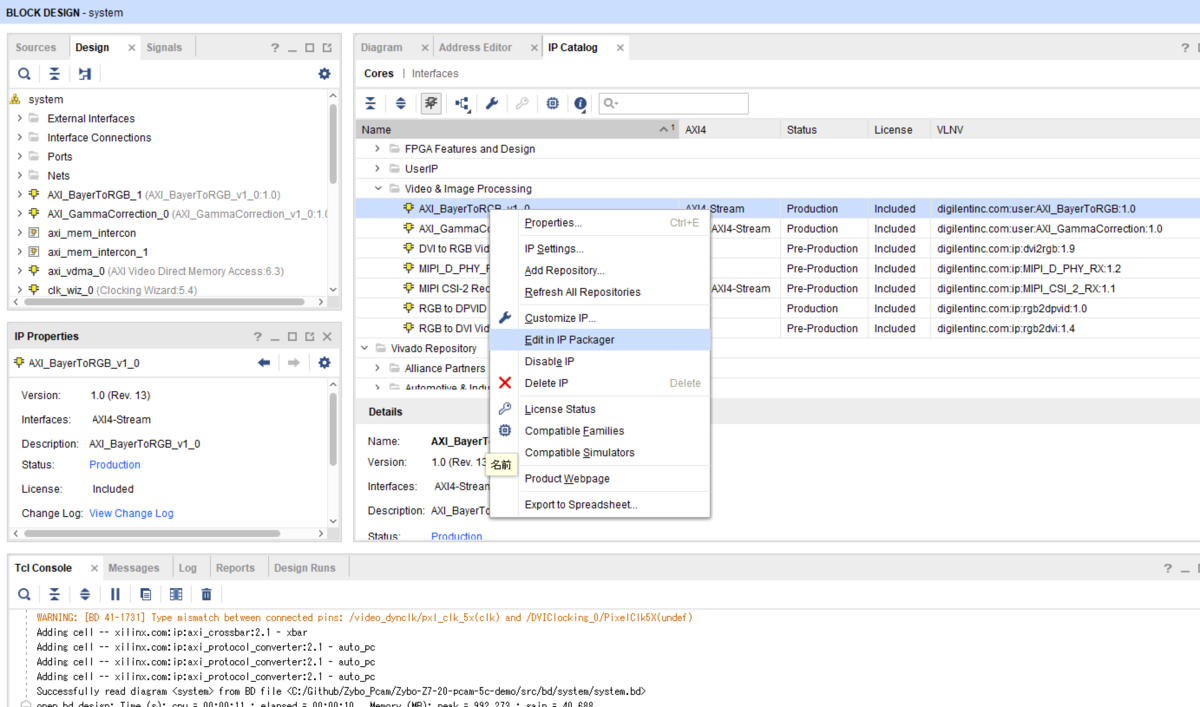

まずProject ManagerにあるIP Catarogを開きます.Video&…のBayerToRGBを右クリックしEdit in Packagerを選択するともう一個Vivadoが開きます.

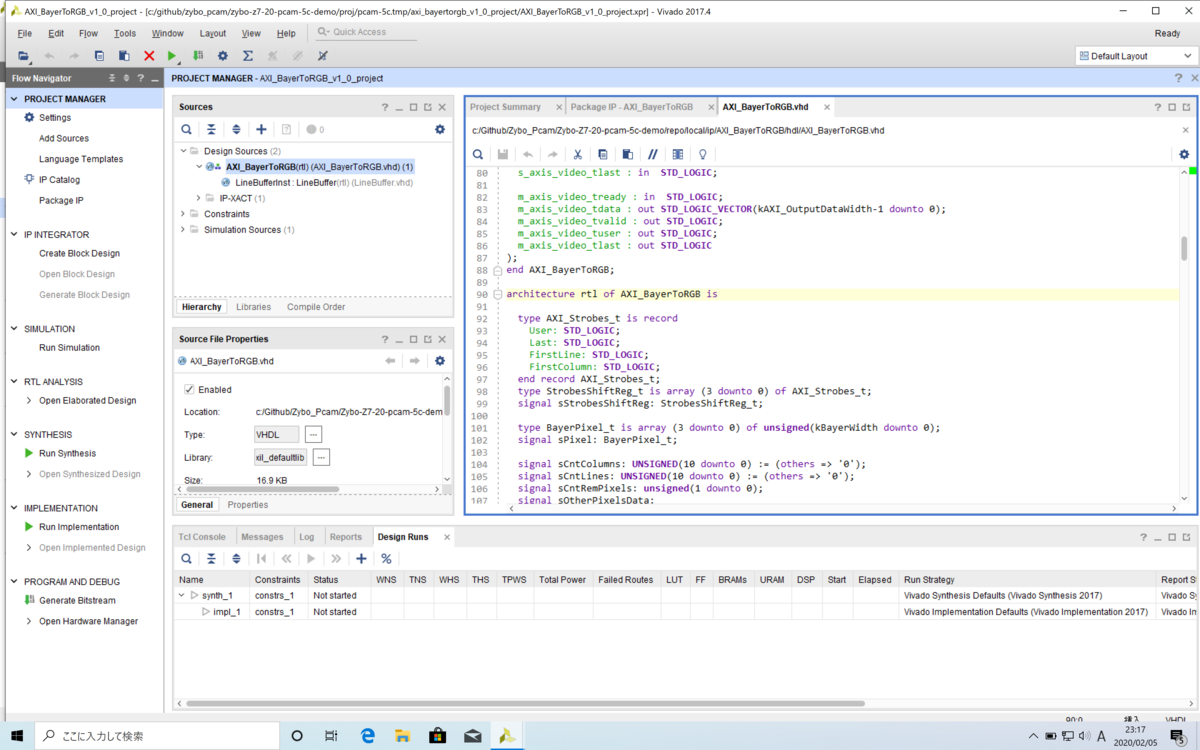

開いたVivadoでAXI_BayerToRGB.vhdを開くとこのようになります.これがIPの本体ですね.ここで買いた内容が反映されるというわけです.

実際に編集しな内容はGithubにあげてあるのでみてください.制約ファイルの関係や自分は他にも機能を追加しているのでちょっとコードが違うかもしれないですが,やりたい機能を追加してみてください.

IPを編集しても反映されない問題について

ここでVivadoの罠があります.IPを編集して保存して論理合成してやったーできたーとそうやすやすといきません.このまま論理合成やってみるとIPで書いた内容が何も反映されません.なんで?

しばらく調べてみるとこのような記事を発見しました.なるほど,そのまま論理合成するだけでは前のファイルが使われてしまって書き換えたファイルが使われずダメらしい.ここで提案されているようにやってみます.

Package IPする

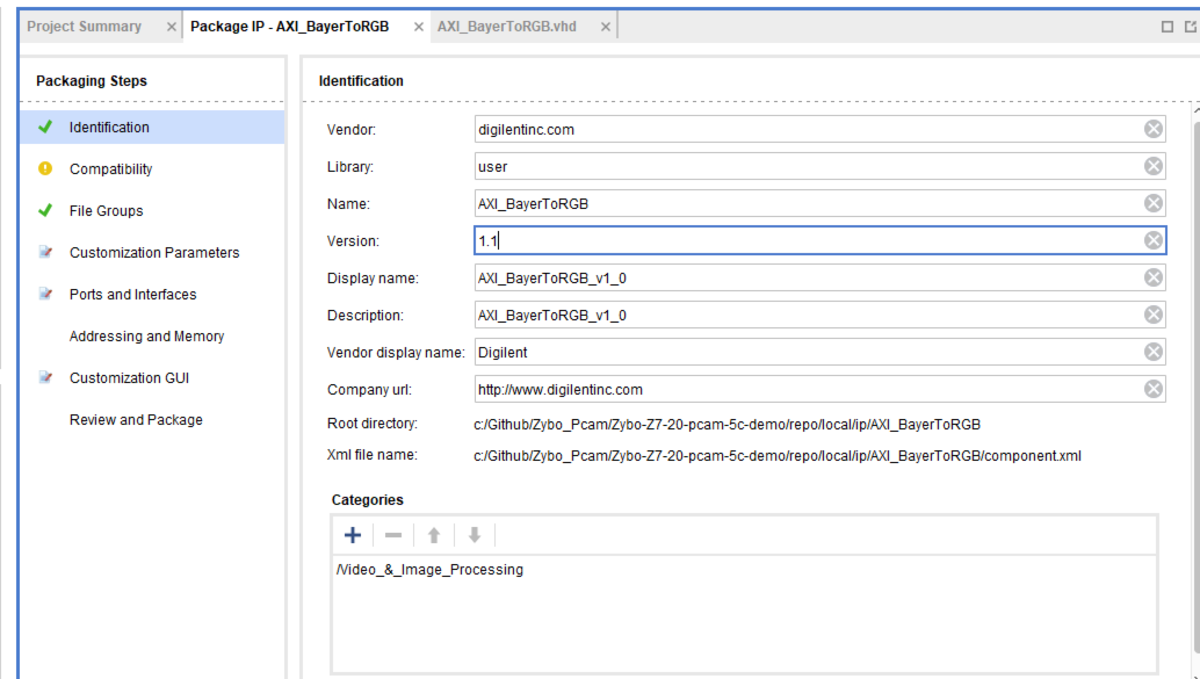

このステップが非常に重要で,Versionを書き換えることでVIvadoに別ファイルであることを認識させます.これを書き換えないとVIvadoはIPが編集されていようと更新しません.やばすぎる...

PackageIPタブに行ってVersionを適当に書き換えます.1.0だったので1.1にしておきました.

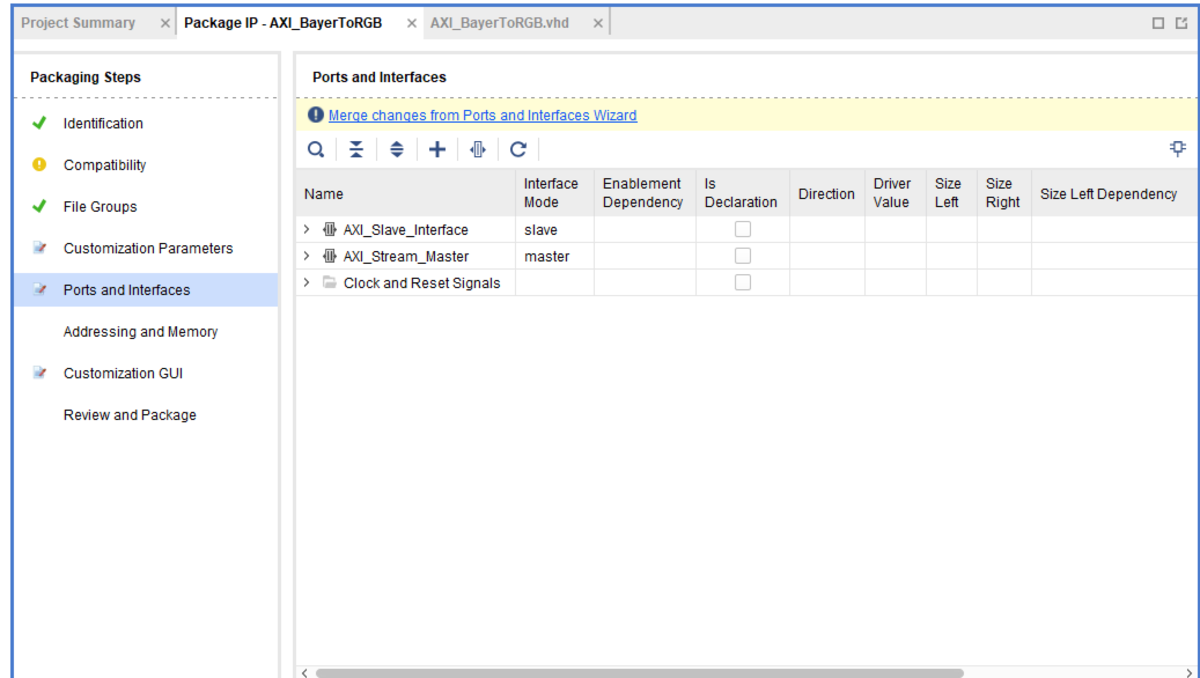

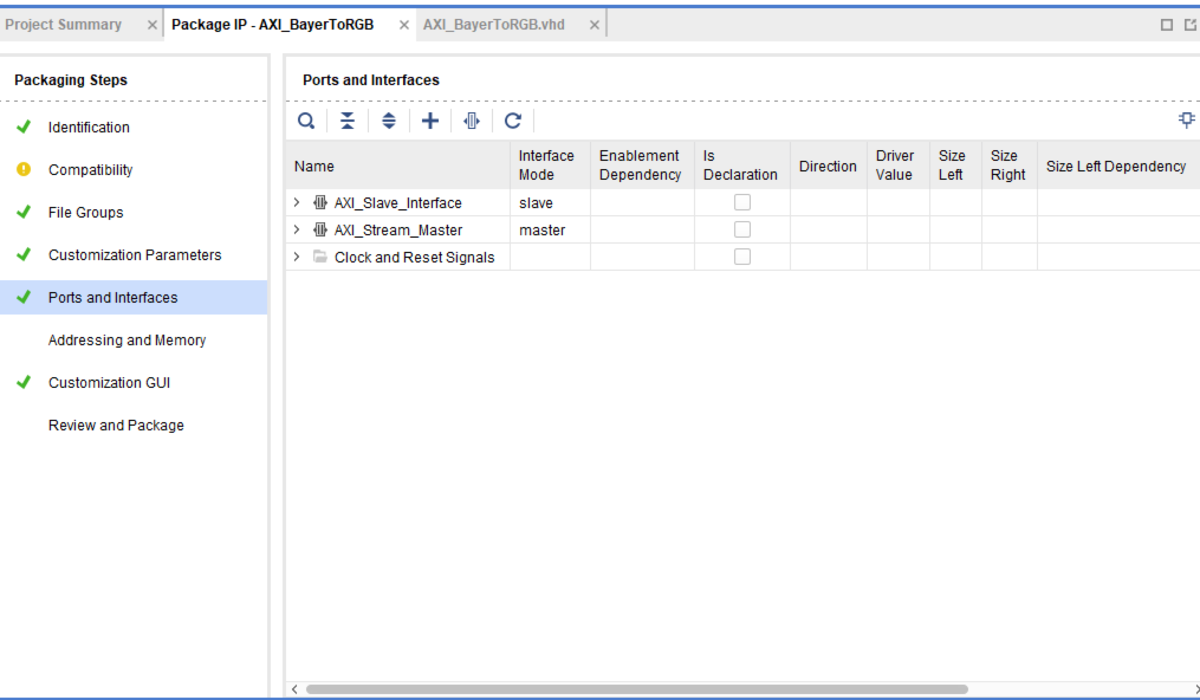

そしてPorts and Interfacesの上の方にあるIP has been modifiedをクリックします.なんかクリックしてほしそうにしてるじゃん?クリックするとPackaging stepsがチェックになると思います.基本的にこのステップに沿ってやっていけばいいです.

最後にreview and packageの下の方にあるPackage IPをクリックします.これでIP編集内容が反映されます.IP編集用のVivadoが閉じて元に戻りました.

IPを再生成する

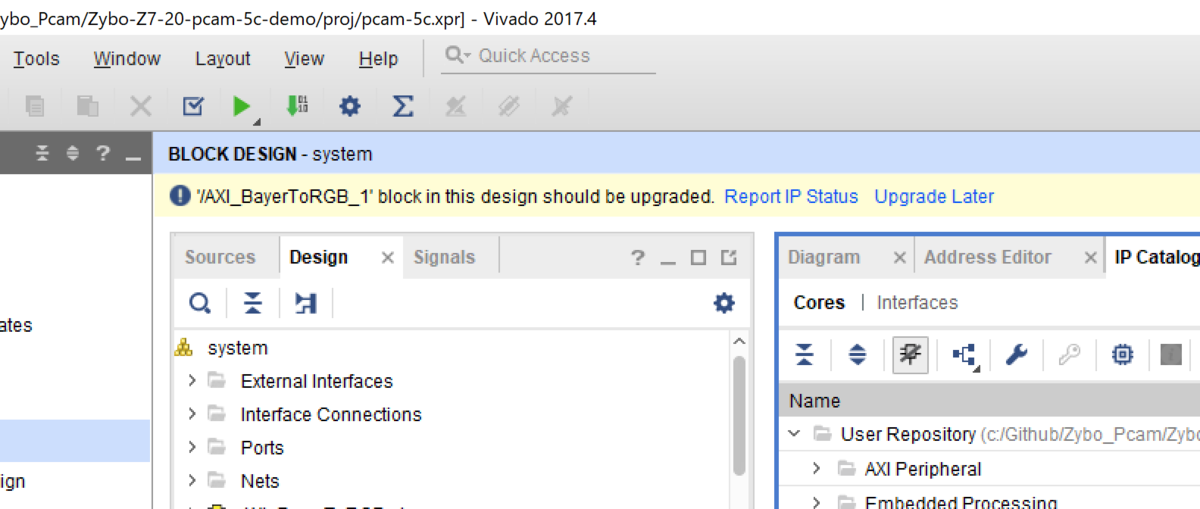

そうすると戻った先の上にまたクリックしてほしそうな奴があるのでReport IP Stausをクリックします.

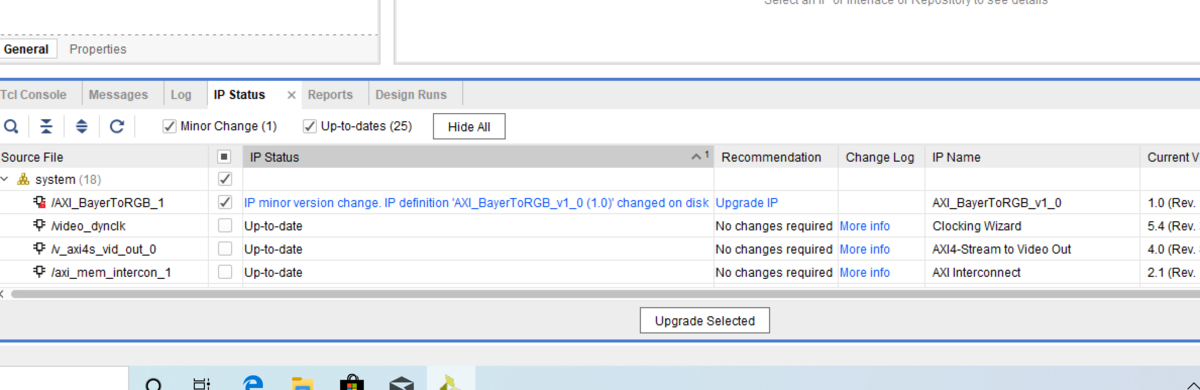

するとさっき編集したIPをUpgradeしろってなるのでチェックされてることを確認してUpgradeをクリック.そうするとIPをGenerateするダイアログが出てくるのでクリック.これで再生成が行われます.

再度Bitstreamを生成する

最初のようにFlow Navigaterから再度BitStreamを生成します.再生成したIPを使ってBitstreamが生成されます.

再度SDKで書き込む

最初のようにSDKでFPGAに回路を書いて,run as からArmを動かします.これで反映される..はずです.

やっぱり反映されない場合

やっぱり反映されない場合もあります.実際自分がやっている中でも反映されないことがありました.辛い.こういう時は一度生成されたIPを編集してない奴した奴もろとも削除してやって全部再生成することで解決する場合があります.ただしこのやり方は全部消して最初からやり直すので生成に時間がかかります.

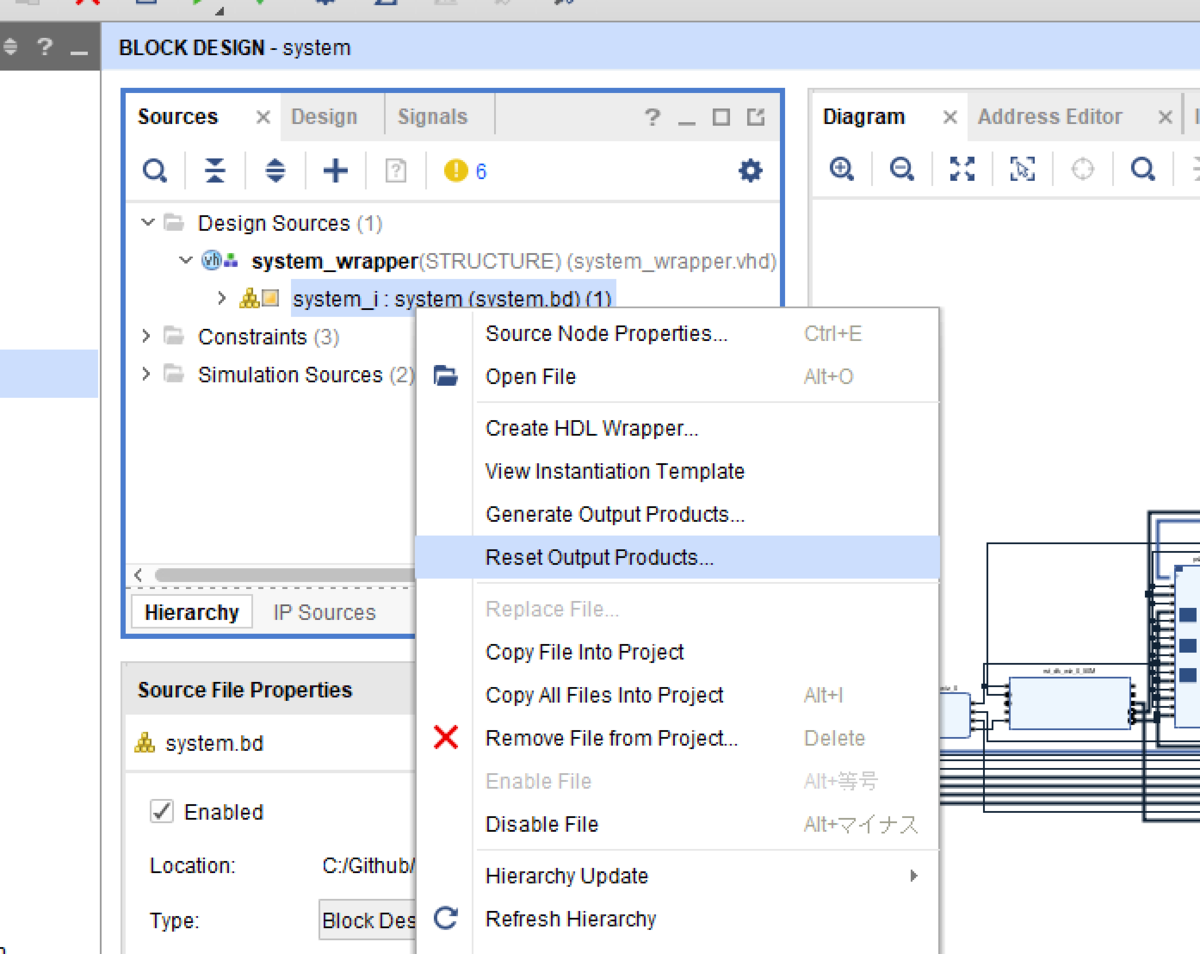

Sourcesのsystem.bdを右クリック,Reset Output Productsをクリックします.これで生成されたIPやらが全部消えます.

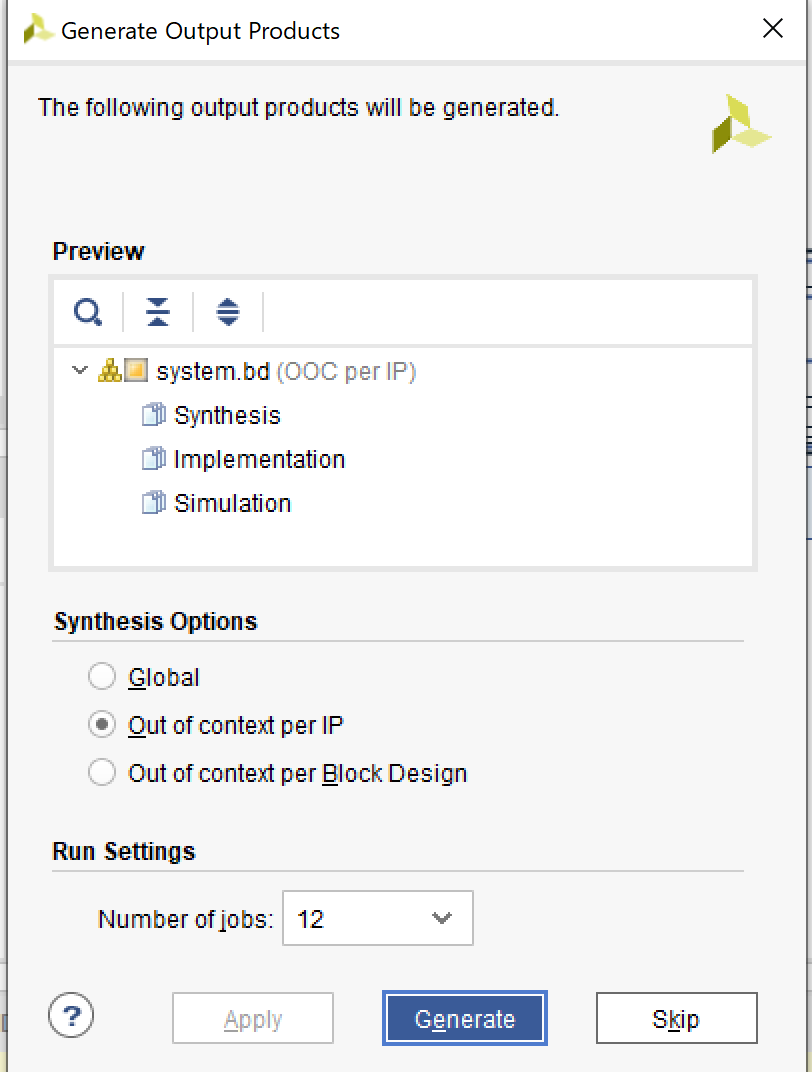

削除が全部終わったら再度system.dbを右クリック,generate output productをクリックします.これでもう一度全部再生成されます.とても時間がかかりますが,コーヒー飲みましょう.実機ではなくシュミレートする大事さがわかりますね.大掛かりな回路になると論理合成するだけで6時間くらいかかるんだとか.

Vivadoが落ちたりするかもしれないけどめげずに頑張りましょう.自分は1日に30回以上落としてました.IP再生成してる時に落ちると,最悪,変な状態で更新が止まってどうにもならなくなることがあるので定期的にGitなどにコミットしておきましょう,怖いぞ.(1敗)

余談ですが自分は仮想環境でWindowsを動かしています.仮想環境が正しくシャットダウンできず,再度起動しようとしたら仮想環境のディスクが壊れました.もちろんVivadoもろともWindowsごと飛びました.ホストはMacBookなのでTimeMachineで差分バックアップ毎日取ってたおかげで命拾いしました...Vivado2017 on Windows 10 on Parallels on MacBook Proは流石にやばい.

ちなみに壊れたのは発表4日前で流石に肝を冷やしました.仮想環境使ってる各位は気を気をつけましょう!!!コードはGitにあげる!バックアップは毎日とる!ハードウェアはサブ機を持つ!これだけでだいぶ心の余裕が違います.

論理合成

ResetしてGenerateした後は同様にBItstreamを生成してSDKでFPGAに書き込んでArmを動かします.これで動くようになるはず.これは赤っぽいところを全部真っ赤に塗りつぶした奴.ちゃんと意図した動作になってますね.FPGAはピクセルを受信すると同時に色が処理されるので遅延が0フレームです.これで世界最速のカラーキーシステムができました.やったね.